This is the first piece of a new series exploring how AI is reshaping the physical world, one industry at a time.

We’ve seen this play out before.

Software went from code to deployment in minutes, thanks to GitHub and AWS.

Design became collaborative and real-time with Figma.

Startups began shipping products at speeds once reserved for big tech.

Now, it’s hardware’s turn.

After decades of slow, manual workflows, chip design is finally getting its Copilot moment, powered by AI. What once took hundreds of engineers and over a year can now be done in days with AI tools that can generate layouts, catch bugs, and even write RTL code.

The semiconductor industry, long considered unshakeable, is entering a new era of AI-native tooling — and the shift is already underway.

From Mylar Sheets to Oligopoly

In the 1970s, chip design was a painstaking craft. Engineers literally drew circuits on Mylar sheets. Verification was done manually, designs were reviewed line by line.

As chips grew more complex, so did the need for the tools needed to build them. Then Electronic Design Automation (EDA) took over moving design to software, where logic became code and simulations replaced hand checks.

Fun fact: The first microprocessor, Intel 4004, was hand-drawn with 2,300 transistors. Today’s chips, like Apple’s M2 Ultra, have over 134 billion transistors. That is a 58 million× leap in complexity.

By the 1990s, Synopsys, Cadence, and Mentor Graphics (later Siemens) consolidated their dominance; today they are responsible for over 70% of EDA sales.

Magma IPO’d in 2001, only to be acquired by Synopsys, a decade later. Dozens of upstarts tried to break through. Most met one of two fates: acquisition or failure.

So, why are there so few winners? Here’s our take:

- Risk aversion: One design error can ruin a $100M tapeout.

- Fab lock-in: Top foundries like TSMC have tight partnerships with the "big three" EDA vendors and certify only a few toolchains. More on this here.

- Relationship-driven sales: Tool adoption is about trust as much as tech.

AI won’t magically erase these barriers. But it can find cracks in the wall.

Why Now?

So why is AI finally shaking up chip design after decades of stasis? Three shifts collided:

- Making chips is now easy:

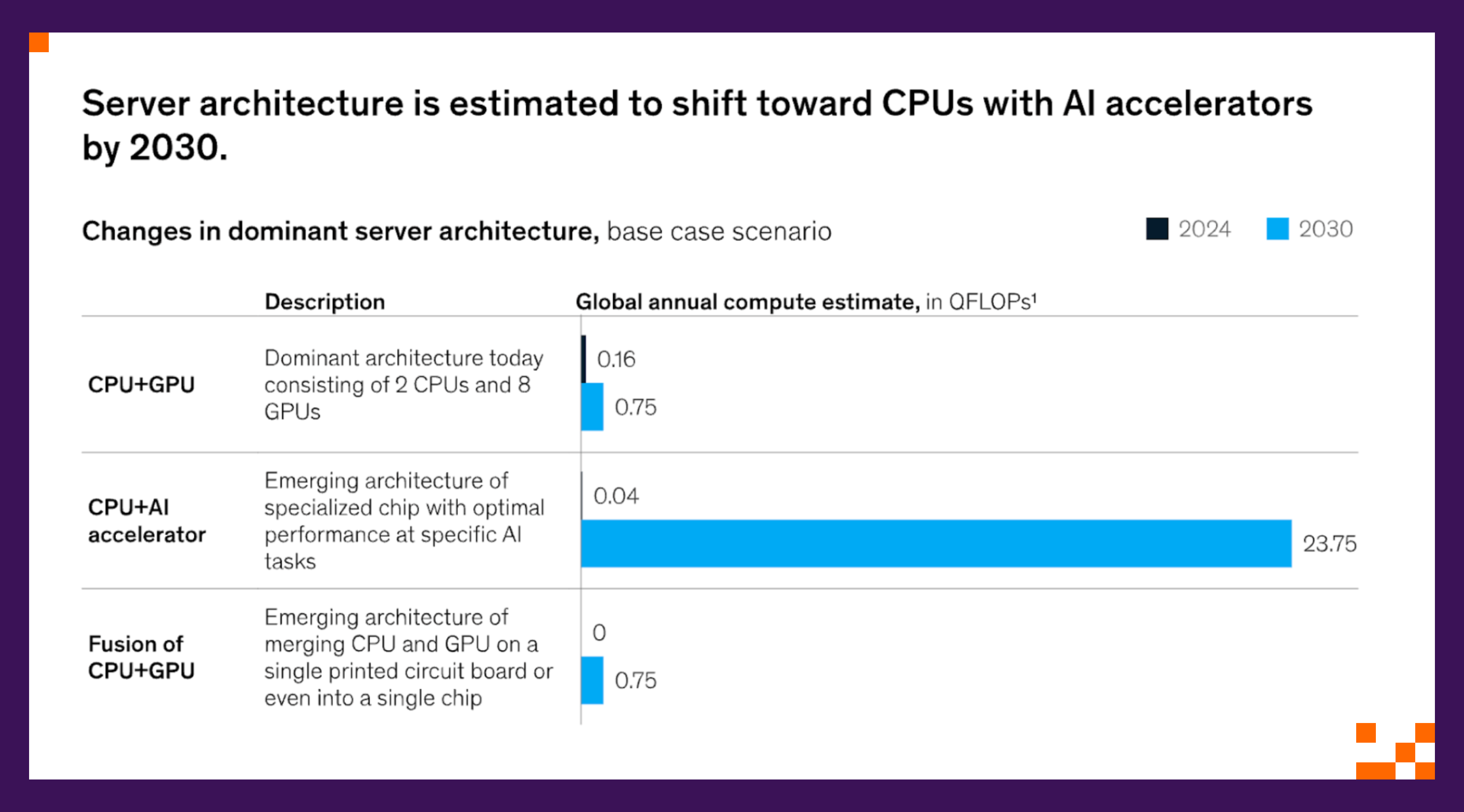

A decade ago, only giants like Intel, NVIDIA, and AMD could make chips. Today, with increased compute requirements, AI-hungry startups are building custom silicon for AI workloads. But they can’t afford $50K‑a‑seat EDA tools or 3‑year design cycles.

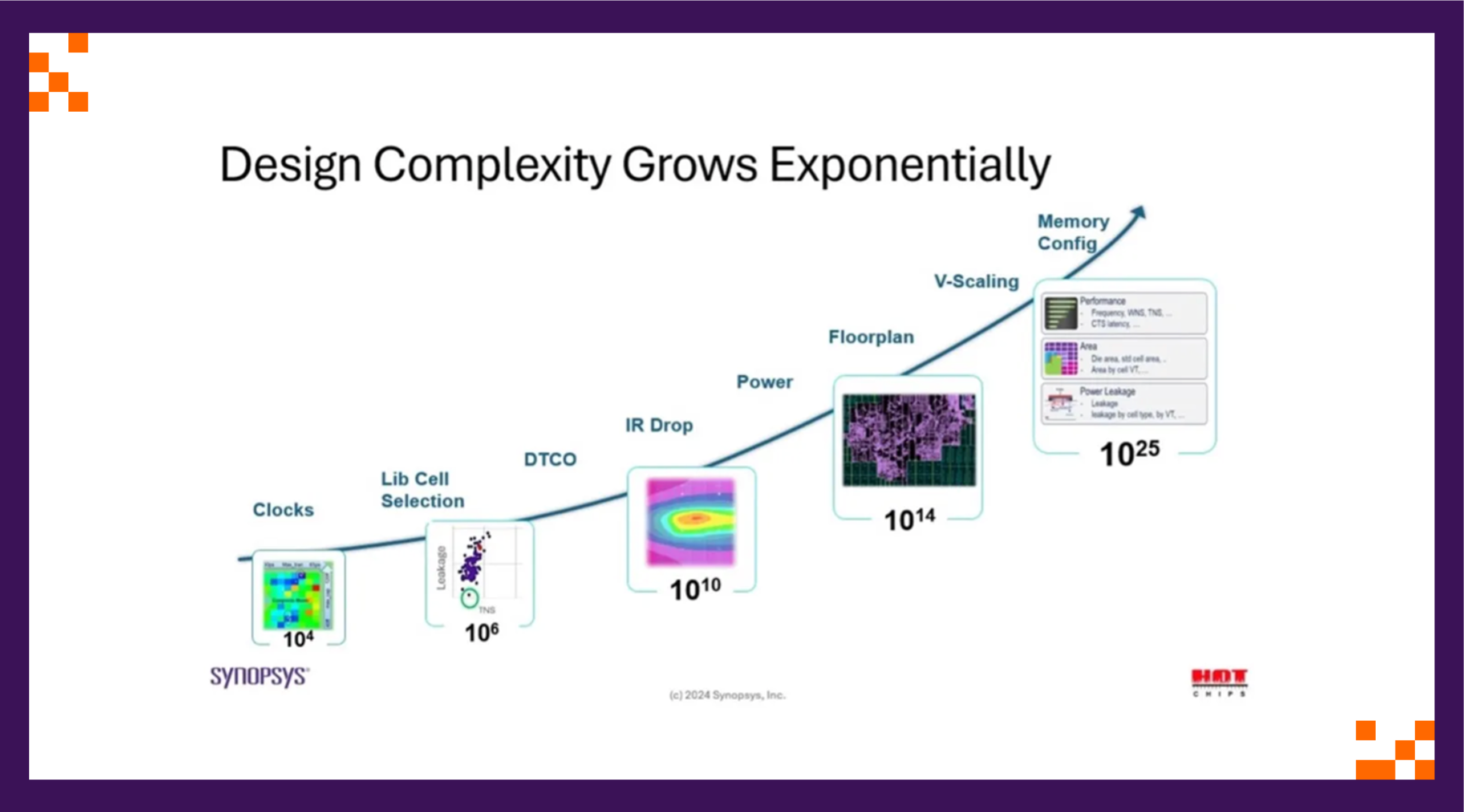

2. Old processes can’t keep up

Design productivity has not kept up with chip complexity: SoCs now pack billions of elements. Verification is slow, manual and hit-and-trial. When time-to-market is king, any tool that cuts weeks or months off the design cycle will win.

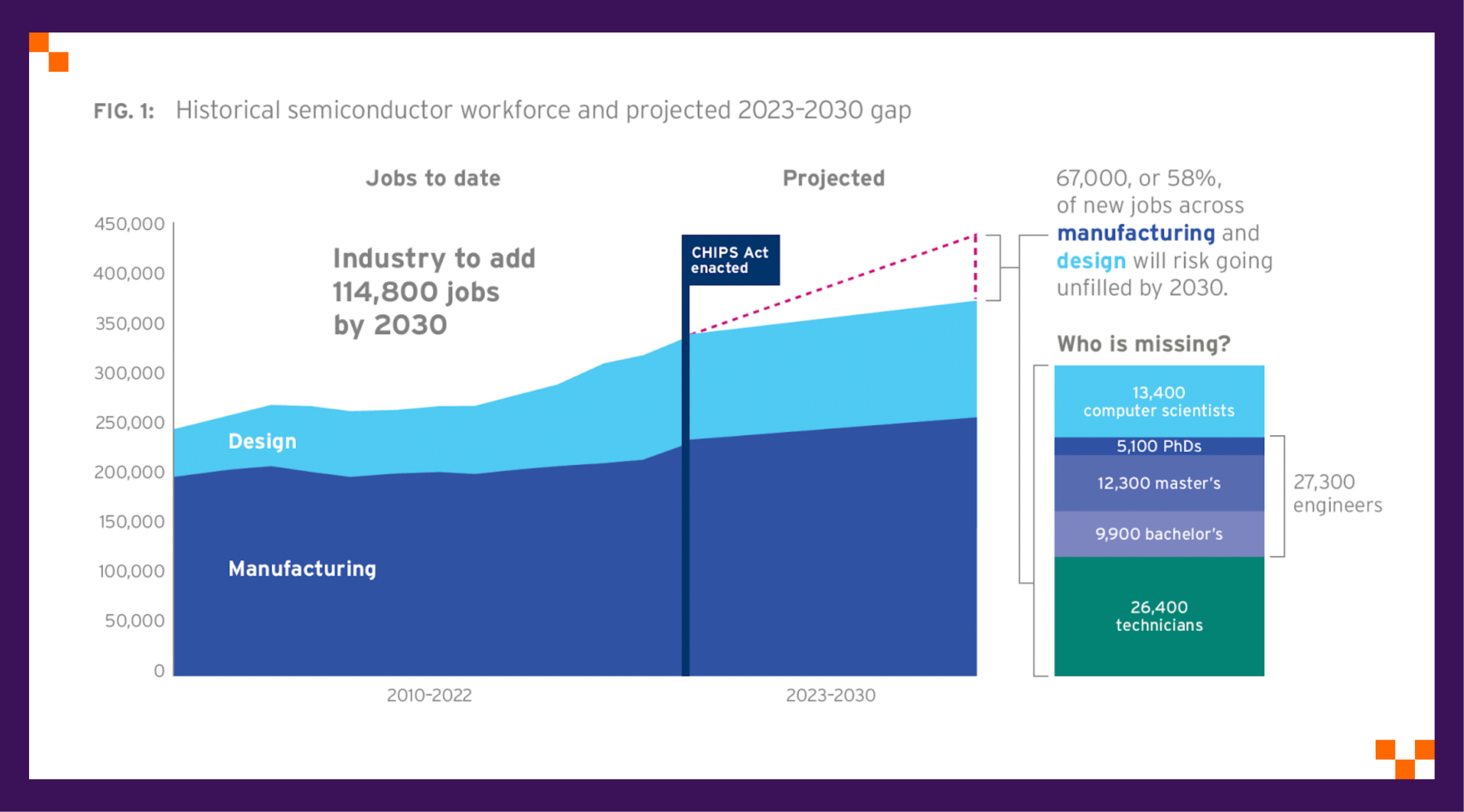

3. The industry is faced with a global talent shortage

According to this Forbes piece, the semiconductor industry will need 1 million additional skilled workers by 2030. Fewer students, an ageing workforce, and rising chip demand are only increasing the gap. AI can reduce the designer-to-verification-engineer ratio from 1:6 to 1:1.

As NVIDIA’s CEO, Jensen Huang put it: “The future of chip design is one human surrounded by hundreds of AIs.”

How can AI solve these bottlenecks?

Finding better designs, faster

AI can explore billions of possible configurations far beyond human capacity. Synopsys’ DSO.ai runs thousands of simulations to improve PPA (power, performance, area), cutting timelines by months.

Learning from iterationGoogle DeepMind’s AlphaChip used reinforcement learning to floorplan chips in under six hours, outperforming humans on wire length and layout efficiency. This is a big deal, suggesting we’re nearing an era of AI-autonomous physical design.

GenAI as an assistant

Cadence’s ChipGPT can interpret specs, generate HDL code, and suggest fixes, freeing engineers for higher‑level decisions. While useful for productivity, it’s not yet proven for creative, from‑scratch HDL generation.

Where the opportunity lies

While the incumbents continue to evolve their tools, startups may be better positioned to take bold, focused bets on how AI can reshape chip design from the ground up.

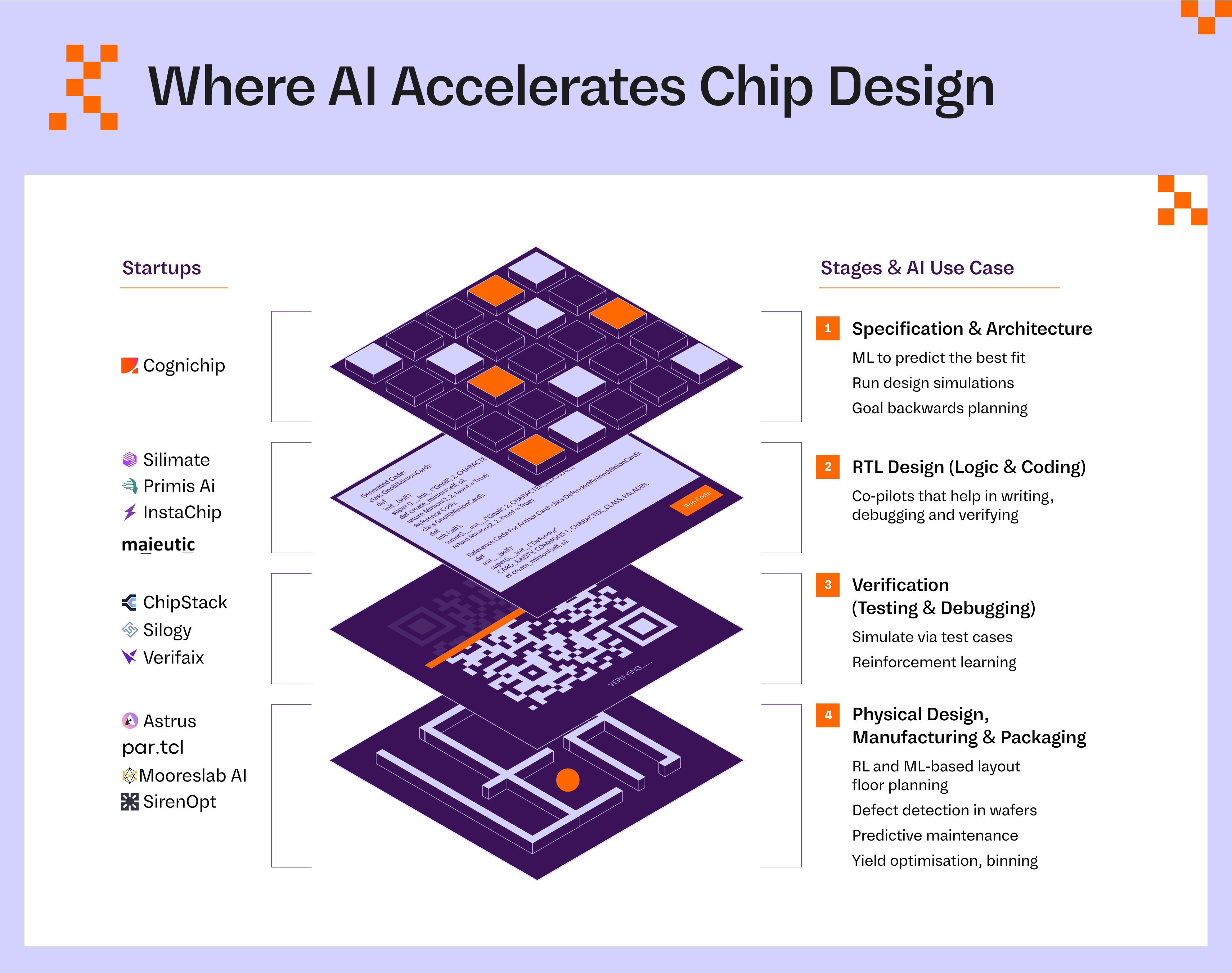

By breaking down the chip design cycle, we can identify the key areas where startups are driving innovation:

1. Specification & Architecture

This is the idea stage: defining what the chip should do, which processing units it needs, memory size, and special features. AI can act as a smart assistant, exploring different architecture options much faster than a human.

- Cognichip is building what it calls “Artificial Chip Intelligence (ACI)”, a foundation AI model for chips. They raised $33 M seed round led by Lux Capital and Mayfield. The founder, Faraj Aalaei (who has taken two chip companies public), says his vision is to cut development time by 50% and costs by 75% using AI.

Our View

This is a promising area for companies building chips from scratch or working on completely new designs. However, large semiconductor companies typically build on top of well-established architecture families, limiting the need for new design exploration.

2. RTL Design (Logic & Coding)

The architecture becomes code in hardware description languages like Verilog or VHDL. It’s a painstaking process, often involving millions of lines of code and endless reviews to catch bugs.

The RTL design stage has seen the most startup activity, with multiple young companies building AI-driven design tools:

- ChipStack uses LLMs to suggest code as the designer types, auto-complete the wiring of signals, and generate test benches for verification.

- Silimate is building an AI assistant that can find functional bugs in the design and performance violations. They recently brought on Tenstorrent as a customer.

- Maieutic Semiconductor, an Indian deep-tech startup, is building an AI copilot specifically for analog chip design which is still a 75% manual process. They recently raised a $4.15 M seed round co-led by Endiya Partners and Exfinity Venture Partners.

Our View

We believe front-end design will remain human-led as Generic RTL copilots are already robust. The opportunity is in context‑aware AI that understands the chip’s constraints and design goals.

3. Verification (Testing & Debugging)

After and during the design coding, verification engineers write and run tests to check every aspect of the chip’s logic against the specifications. This is heaviest lift in chip design: ~70% of total effort and highly repetitive. AI can help simulate and test all the important scenarios, often missed by traditional coverage metrics

- Silogy’s AI agent “Viv” can diagnose the root cause of test failures in minutes, helping bring new chips to market up to 10× faster.

- Verifaix is building AI agents for spec analysis, testplan/testbench generation, and debug, automating various parts of the verification flow.

Our View

The most promising wedge: Verification workflows command nearly 70% of design effort, are standardised, data-rich and painful, therefore ripe for automation. If an AI tool can truly improve test coverage, detect errors earlier, and speed up debugging, companies will be eager to adopt it as an additional layer on top of their existing workflows.

4. Physical Design, Manufacturing and Packaging

At this stage, the chip moves from logic to physical reality, converting code into a geometric layout of transistors and wires through place-and-route. AI, especially reinforcement learning, can optimise this layout for Power, Performance, and Area (PPA) far faster than human engineers.

Once the design is finalised, it's sent to fabs (like TSMC) for manufacturing, where AI helps spot defects early using sensor and test data. Finally, during packaging, AI assists in planning multi-die layouts, predicting heat/stress risks, and routing complex inter-chip connections.

- Astrus automates analog layouts to instantly generate a workable transistor layout, compressing timelines by months. Founded in 2022, Astrus raised a $2.4 M pre-seed led by Khosla Ventures in 2023.

- SirenOpt is building an AI-powered quality control platform. Using their novel sensor technology plus machine learning, they can monitor material properties in real time on production lines, detecting subtle variations or defects that traditional tests miss.

Our View

This layer is hard to build for, but if cracked, it offers deep moats and sticky customers.

- Using AI for physical design is real, where companies like Google have published papers showing RL-based floorplanning outperforming human results. Startups here must show clear PPA wins to succeed.

- Manufacturing AI depends on tight fab integration and data access, which is a tough moat to break for new entrants unless they partner with a foundry or EDA giant.

- Packaging AI is still emerging, but growing in importance with multi-die architectures becoming mainstream. Tools that can help model and optimise 3D chiplets and thermal flows have a clear edge.

Watch-outs for founders

Here are the key things that a founder starting in this space should think about:

- Don’t build what generic LLMs will soon match

Over time, general-purpose LLMs will ingest similar data and close the gap. Founders should focus on chip-specific workflows or agents that generic LLMs cannot easily replicate. The co-pilot universe is increasingly becoming a winner-takes-all market. - Avoid going head on against EDA giants

Instead, find a narrow wedge: a use case or workflow where EDA tools are weak or slow-moving, and build on top of the existing ecosystem. Bring them in as early partners, not adversaries. - Co-design with 2–3 anchor customers

This is not a “build in isolation and launch” kind of market. Semiconductor teams have highly specific needs, and success requires a customer-centric approach. Founders should partner with a few deep-tech teams early on and co-develop the solution with real users. - Ship fast with the right team

The space is highly dynamic, so show real results, fast. Build a team around deep EDA domain knowledge and AI expertise, and bridge the two worlds.

Summing Up

AI for chip design isn’t “push a button, get a chip.” It’s re-engineering the loop between idea and output, collapsing months into weeks, freeing engineers from drudgery, and embedding intelligence into every step of the process.

By 2035, designing a chip should be no harder than building any other hardware product. The architecture will be sketched out on a napkin. A three-person team drafts specs on a whiteboard. An AI assistant compiles, verifies and simulates the design in hours. The foundry tapeout process gets significantly streamlined. The whole process takes a few months — a process that once took years.

This isn't a theory. AI is already inside chip teams at Nvidia, AMD, and every ambitious startup. Billions in funding are flowing into AI-EDA.

Founders, engineers, skeptics: what do you see coming next?

Where will AI crack the cycle first?

Will verification be the wedge, or will another stage break open sooner?

Will the big three out-build, or just out-buy, the next wave?

At Z47, we invest in dev tools for the physical world: semiconductors, aerospace, energy, manufacturing, and robotics. If you’re building in this space, write to us at physical.ai@z47.com.

.jpg)

%20(1).png)

.svg)

.png)